Tasarımlarda kullanılan saat kaynağından daha yavaş çalışan, daha düşük frekanslı saat kaynaklarına ihtiyaç duyulur. Bu durumda kullanılabilecek çeşitli yöntemler mevcuttur. Örneğin; FPGA üreticileri tarafından sağlanan PLL (Phase Locked Loop), DCM (Digital Clock Manager) gibi hazır tasarım kütüphaneleri kullanılabilir. Bu yazıda IP Core üzerinden saat kaynağı üretilecek.

- Sürümler:

- XILINX ISE Design Suite 14.7

- LogiCORE IP Clocking Wizard 3.6 (ISE)

- Saat Üreteci Sihirbazı

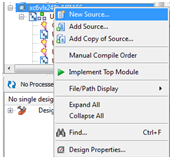

ISE ekranında açılan pencerede tanımlı FPGA üzerine sağ tıklanarak New Source seçilir (Şekil 1).

Şekil 1: New Source seçimi.

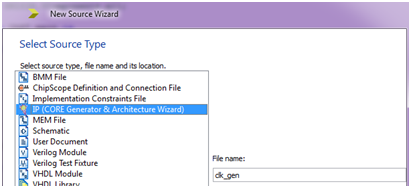

Saat üreteci için IP(CORE Generator & Architecture Wizard) seçilir. Dosya ismi ve lokasyonu seçildikten sonra devam edilir (Şekil 2).

Şekil 2: IP ekleme.

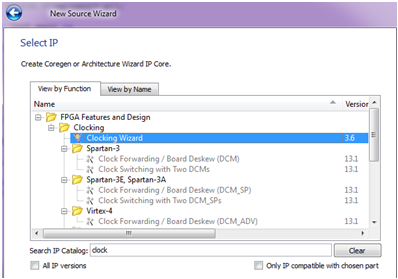

IP seçimi seçimi için Search IP Catalog dan "clock" araması yapılır ve Clocking Wizard seçilir (Şekil 3).

Şekil 3: Clocking Wizard seçimi.

- Saat Üreteci Özellikleri

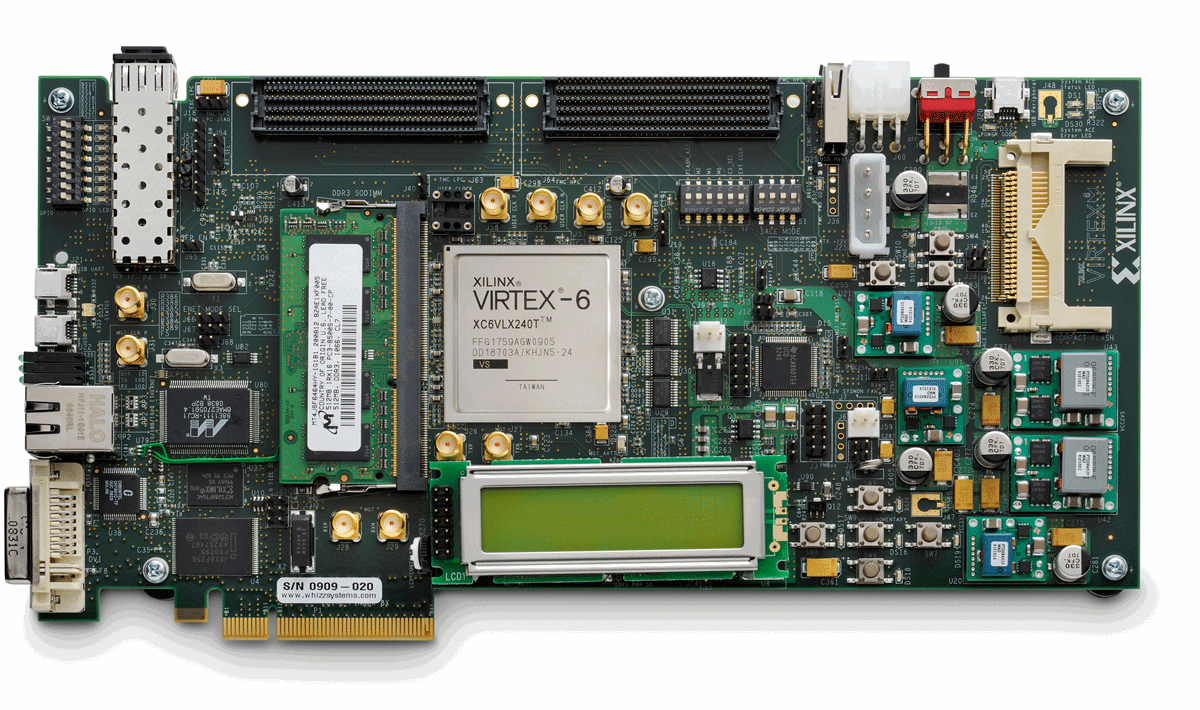

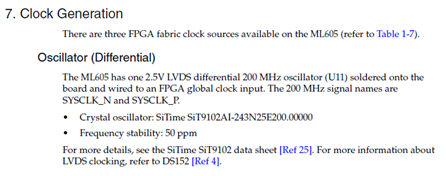

ML605 geliştirme kartının üzerinde 200MHz osilatör (diferansiyel) olduğu ug534 dökümanında gözükmektedir (Şekil 4).

Şekil 4: ug534 dökümanı clock generation bölümü.

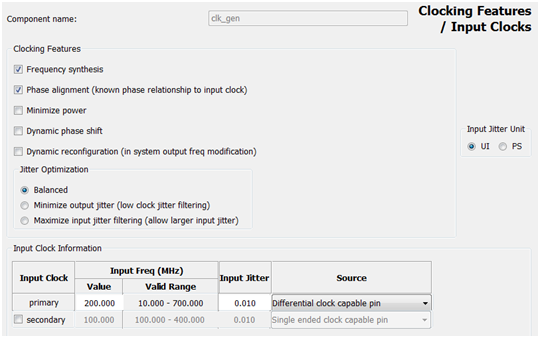

Açılan clocking wizard ekranında saat için giriş frekansı değeri 200.000 olarak girilir. Kaynak ise, osilatör diferansiyel olduğu için (Şekil 4) "Differantial clock capable pin" olarak seçilir (Şekil 5).

Şekil 5: Saat üreteci özellikleri.

- Frequency synthesis: Bu özellik, çıkış saatlerinin aktif giriş saatinden farklı frekanslara sahip olmasını sağlar.

- Phase alignment: Bu özellik, çıkış saatinin bir cihazın giriş saati pini gibi referansa faz kilitli olmasını sağlar.

- Minimize power: Bu özellik, frekans, faz kayması veya görev döngüsü doğruluğu olasılığı pahasına primitive için gereken güç miktarını en aza indirir.

- Dynamic phase shift: Bu özellik çıkış saatlerinde faz ilişkisini değiştirmenize izin verir.

- Dynamic reconfiguration: Bu özellik, cihaz yapılandırmasından sonra ilkelin programlamasını değiştirmenize izin verir. Bu seçenek seçildiğinde, saat sihirbazı M, D ve CLKOUT [0: 6] _DIVIDE için yalnızca tam sayı değerlerini kullanır.

- Balanced: Yazılımda, titreşim optimizasyonu için doğru BANDWIDTH seçerek Dengeli sonuçların seçilmesi.

- Minimize output jitter: Bu özellik çıkış saatlerinde titreşimi en aza indirir, ancak güç pahasına ve muhtemelen çıkış saati fazı hatası ile sonuçlanır. Bu özellik, Maximize input jitter filtering' ile kullanılamaz.

- Maximize input jitter filtering: Bu özellik, giriş saatlerinde daha büyük girdi titremesine izin verir, ancak çıkış saatindeki titreşimi olumsuz olarak etkileyebilir. Bu özellik 'Minimize output jitter' ile kullanılamaz.

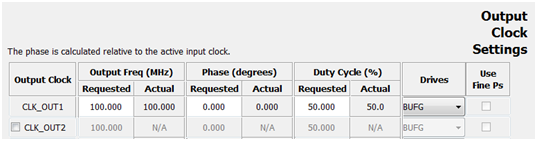

Saat üretecinin çıkış için örnek olması amacıyla çıkış frekansı 100.000 olarak girilir (Şekil 6). Faz hizalaması "phase alignment" seçilirse, faz kayması aktif giriş saatine göre değişir. Faz hizalaması "phase alignment" seçilmemişse, faz kayması CLK_OUT1'e göre değişir.

Kullanılabilecek buffer cihazınızın ailesine bağlıdır. Çıkış sürücüsü olarak BUFR'a sahip tüm çıktılar için, "BUFR_DIVIDE" özeliği HDL'de genel bir parametre olarak mevcuttur. Kullanıcı tasarım örneği oluştururken BUFR'ın bölme değerini değiştirebilir.

Şekil 6: Saat çıkış ayarları.

- Geribildirim ve I/O

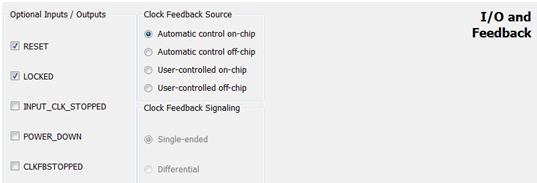

I/O and Feedback seçenekleri Şekil 7'de ki gibi seçilir. Geri besleme seçimi yalnızca faz hizalaması seçildiğinde kullanılabilir.

"Phase alignment" seçilmediğinde, çıkış geribildirimi doğrudan giriş geri beslemesine bağlıdır. Faz sıralamalı tasarımlar için, geri besleme yolunun CLK_OUT1 için ekleme gecikmesiyle uyuşmasını istiyorsanız, "Automatic control on-chip" seçin. Geri bildirim harici bir koddaysa, "User-controlled" seçebilirsiniz. Path FPGA üzerinde tamamen bulunuyorsa, "on-chip" seçin; aksi takdirde, "off-çipi" seçin.

Harici geri besleme ve ilgili I/O mantığı gerektiren tasarımlar için, "Automatic control off-chip" geri besleme'yi seçin. Bu modda tek uçlu veya diferansiyel geribildirim seçebilirsiniz. Sihirbaz, geri besleme sinyallerini I/O'ya yönlendirmek için core logic ve gerekli logicleri üretir.

Şekil 7: I/O and Feedback ayarları.

- Saat Üretecinin VHDL Koda Aktarılması

Bu işlemler yapıldıktan sonra saatimizi üretmek için Generate butonuna tıklanır (Şekil 8).

Şekil 8: Generate butonu.

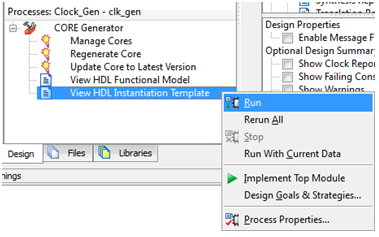

Clock Generator tarafından oluşturulan .xco uzantılı IP'ye tıklanılır. ISE nin Processes sekmesinde Şekil 9'da gösterilen "View HDL Instantiation Template" sekmesine sağ tıklanılır ve Run edilir.

Şekil 9: Clock Generator için Processes sekmesi.

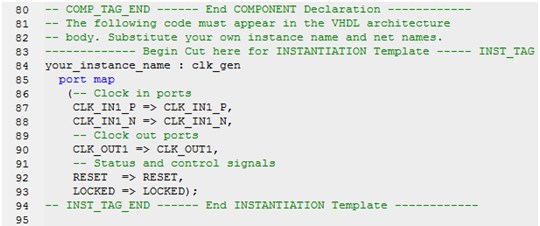

IP tarafından oluşturulan saat üretecinin port map kısmı Şekil 10'da gözükmektedir ve bu bölüm kopyalanıp programınızın main kısmında "Begin" ve "end Behavioral" arasına yapıştırılır.

Şekil 10: Otomatik olarak oluşturulan clock giriş ve çıkışları.

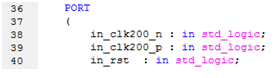

Otomatik olarak oluşturulan saat girişlerini kullanmak için main kısmında diferansiyel hatları için giriş ve reset portu oluşturuldu (Şekil 11).

Şekil 11: Diferansiyel clock hatlarımız için girişler.

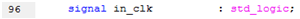

100 MHz saat i kullanabilmek için in_clk adında sinyal tanımlandı (Şekil 12).

Şekil 12: 100Mhz saat sinyalini kullanabilmek için sinyal tipinde in_clk değişkeni.

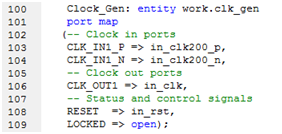

main kısmına kopyalanan clock generator için başına " entity work. " eklenir (Şekil 13). main portlarını ise clock generator ile ilişkilendirmek için Şekil 13'de ki sinyal atamaları yapılır. LOCKED open olarak bırakılır.

Şekil 13: Sinyal atamaları.

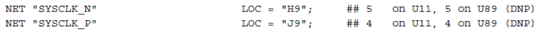

FPGA pin atamaları için ug534 dökümanında Sayfa 93'de clock için pin atamaları gösterildi (Şekil 14).

Şekil 14: ug534 dölümanı clock pin atamaları.

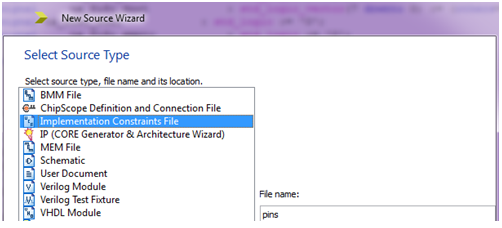

FPGA de uygulamak için pins adında "Implementation Constraints File" IP'den oluşturulur (Şekil 15).

Şekil 15: Implementation Constraints File oluşturma.

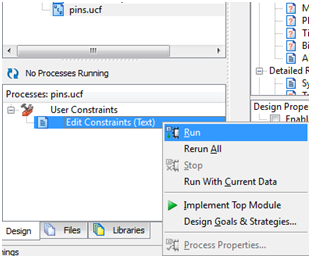

Implementation Constraints File'ı düzenlemek için pins.ucf dizinine tıklanır ve Şekil 16'da ki işlem yapılır.

Şekil 16: Implementation Constraints File için processes sekmesi.

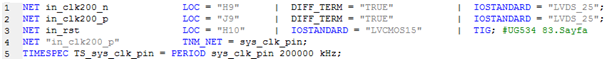

Text kısmı Şekil 17'de ki gibi düzenlenir ve pin atamaları yapılır.

Şekil 17: .ucf de pin atamaları.

Erdem Gökşen

Sayısal Tasarım Mühendisi